Built-in W6100

Support hardwired TCP/IP (IPv4/IPv6, 8 sockets) · 32KB socket buffers

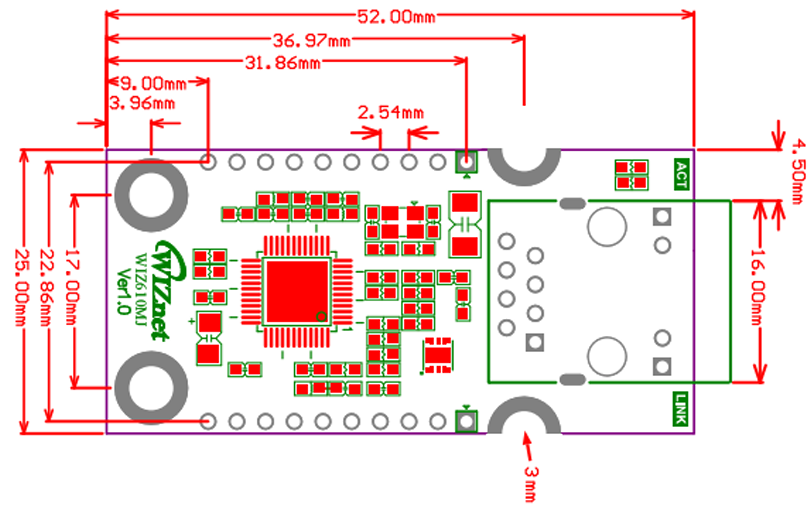

WIZ610MJ is the network module that includes W6100 (TCP/IP hardwired chip, include PHY), MAG-JACK (RJ45 with X’FMR) with other glue logics. Please click the link for the further information about W6100. It can be used as a component and no effort is required to interface W6100 and Transformer. The best advantage of the WIZ610MJ is that it supports IPv6. The WIZ610MJ is an option for users who want to develop their Internet enabling systems rapidly.

Support hardwired TCP/IP (IPv4/IPv6, 8 sockets) · 32KB socket buffers

Support 2×10, 2.54mm header · compact pluggable

Support 8-bit Indirect BUS and Fast-SPI (MODE 0/3)

Support 10BaseT/10BaseTe/100BaseTX Ethernet MACPHY

Support TCP, UDP, IPv4/IPv6, ICMPv4/v6, ARP, NDP, IGMPv1/v2, MLDv1/v2, PPPoE

Support transformer & Link/Act LEDs built-in

Support 32KB configurable allocation for stable throughput

Support 3.3V Operation (2.7V to 3.6V)

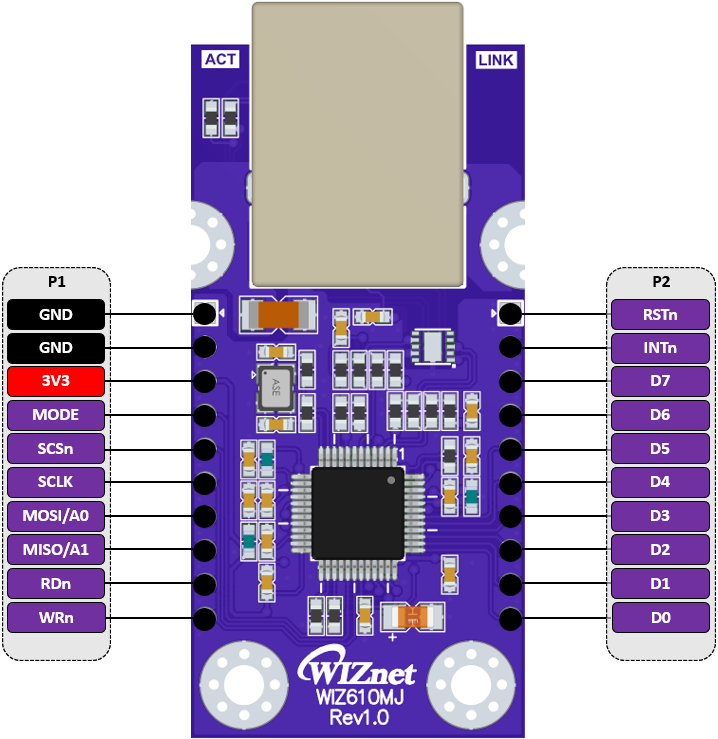

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | P | GND | Ground |

| 2 | P | GND | Ground |

| 3 | P | 3V3D | 3.3 V Power |

| 4 | I | MODE | SPI/BUS Select pin SPI : Low BUS : High |

| 5 | I | SCSn | SPI Chip select (active low) |

| 6 | I | SCLK | SPI Clock input |

| 7 | I | MOSI/A0 | SPI : Master-Out / Slave-In BUS : A0 |

| 8 | O/I | MISO/A1 | SPI : Master-In / Slave-Out BUS : A1 |

| 9 | I | RDn | Read Strobe SPI : indicates Read Operation BUS : indicates Read Operation |

| 10 | I | WRn | Write Strobe SPI : indicates Read Operation BUS : indicates Write Operation |

| Pin | Type | Name | Description |

|---|---|---|---|

| 1 | I | RSTn | Hardware reset (active low, ≥ 1 µs) |

| 2 | O | INTn | Interrupt output (low-active) |

| 3 | IO | D7 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 4 | IO | D6 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 5 | IO | D5 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 6 | IO | D4 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 7 | IO | D3 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 8 | IO | D2 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 9 | IO | D1 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| 10 | IO | D0 | Data Bus pin SPI : DAT [7:0] must be floated. BUS : Data is carried over DAT [7:0] between HOST and W6100 |

| Symbol | Parameter | Pins | Min | Typ | Max | Unit |

|---|---|---|---|---|---|---|

| VDD | Supply voltage | 3.3 V | 2.97 | 3.3 | 3.63 | V |

| VIH | High-level input | ALL | 2.0 | – | - | V |

| VIL | Low-level input | ALL | – | – | 0.8 | V |

| VOH | High-level output | ALL | 2.4 | 3.3 | – | V |

| VOL | Low-level output | ALL | 0.0 | – | 0.4 | V |

| IDD | Supply current (Normal) | 3.3 V | – | 132 | – | mA |

| IPD | Supply current (Power-down) | 3.3 V | – | 13 | – | mA |

| Condition | Min | Typ | Max | Unit |

|---|---|---|---|---|

| 100M Link | – | 98 | 115 | mA |

| 10M Link | – | 112 | 265 | mA |

| 10M-Te Link | – | 75 | 190 | mA |

| 100M Unlink | – | 50 | 199 | mA |

| 10M Unlink | – | 26 | 170 | mA |

| 10M-Te Unlink | – | 26 | 130 | mA |

| Un-Link (Auto-negotiation mode) | – | 50 | 199 | mA |

| Power Down mode | – | 14 | 20 | mA |

| Name | Description | Notes | |

|---|---|---|---|

| Datasheet | Technical datasheet for WIZ610MJ module | WIZ610MJ Datasheet v1.0 |

WIZ610MJ Datasheet v1.0 |